Search Results for author: Keisuke Sugiura

Found 4 papers, 0 papers with code

A Cost-Efficient FPGA Implementation of Tiny Transformer Model using Neural ODE

no code implementations • 5 Jan 2024 • Ikumi Okubo, Keisuke Sugiura, Hiroki Matsutani

To mitigate the computational complexity, recently, a hybrid approach has been proposed, which uses ResNet as a backbone architecture and replaces a part of its convolution layers with an MHSA (Multi-Head Self-Attention) mechanism.

An FPGA-Based Accelerator for Graph Embedding using Sequential Training Algorithm

no code implementations • 23 Dec 2023 • Kazuki Sunaga, Keisuke Sugiura, Hiroki Matsutani

A graph embedding is an emerging approach that can represent a graph structure with a fixed-length low-dimensional vector.

A Low-Cost Neural ODE with Depthwise Separable Convolution for Edge Domain Adaptation on FPGAs

no code implementations • 27 Jul 2021 • Hiroki Kawakami, Hirohisa Watanabe, Keisuke Sugiura, Hiroki Matsutani

It is implemented on Xilinx ZCU104 board and evaluated in terms of domain adaptation accuracy, inference speed, FPGA resource utilization, and speedup rate compared to a software counterpart.

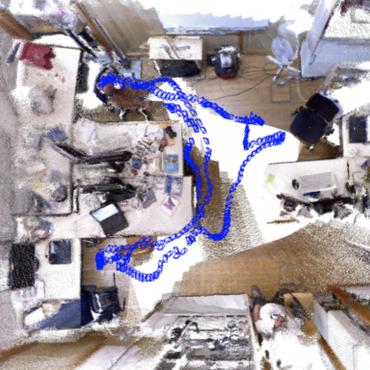

An FPGA Acceleration and Optimization Techniques for 2D LiDAR SLAM Algorithm

no code implementations • 29 May 2020 • Keisuke Sugiura, Hiroki Matsutani

In this paper, we propose a resource-efficient FPGA implementation for accelerating scan matching computations, which typically cause a major bottleneck in 2D LiDAR SLAM methods.